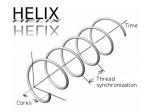

# HELIX-RC An Architecture-Compiler Co-Design for Automatic Parallelization of Irregular Programs

Simone Campanoni, Kevin Brownell, Svilen Kanev Timothy M. Jones, Gu-Yeon Wei, David Brooks

HARVARD School of Engineering and Applied Sciences

# Use multiple cores for a **single** program Distribute **loop iterations** among cores

## Motivation

## Motivation

## Outline

• Evaluation of HELIX-RC

## Outline

• Opportunity of small loops

• Evaluation of HELIX-RC

- Code complexity

- Control flow

- Data flow

- $\Uparrow$  Code complexity

- Control flow

- Data flow

- $\Uparrow$  Code complexity

- Control flow

- Data flow

Dependences to satisfy  $\uparrow$

- Actual

- Apparent ↑

- $\Uparrow$  Code complexity

- Control flow

- Data flow

**Prior Works**

Dependences to satisfy  $\uparrow$

- Actual

- Apparent ↑

## • Thread-Level-Speculation (TLS)

● ↓ Apparent

- $\Uparrow$  Code complexity

- Control flow

- Data flow

Prior Works

- Thread-Level-Speculation (TLS)

- ↓ Apparent

- TLS overhead  $\Rightarrow$  big loops

Dependences to satisfy  $\uparrow$

- Actual

- Apparent ↑

- ↑ Code complexity

- Control flow

- Data flow

**Prior Works**

Dependences to satisfy  $\uparrow$

- Actual

- Apparent ↑

# • Thread-Level-Speculation (TLS)

- ↓ Apparent

- TLS overhead  $\Rightarrow$  big loops (10× more dependences!)

- $\Uparrow$  Code complexity

- Control flow

- Data flow

Actual

Apparent 1

Dependences to satisfy  $\uparrow$

#### Prior Works

- Thread-Level-Speculation (TLS)

- ↓↓ Apparent

- TLS overhead  $\Rightarrow$  big loops (10× more dependences!)

- $\Uparrow$  Code complexity

- Control flow

- Data flow

Dependences to satisfy  $\uparrow$

- Actual

- Apparent ↑

#### Prior Works

- Thread-Level-Speculation (TLS)

- ↓ Apparent

- TLS overhead  $\Rightarrow$  big loops (10× more dependences!)

#### HELIX-RC

- $\Uparrow$  Code complexity

- Control flow

- Data flow

Dependences to satisfy  $\uparrow$

- Actual

- Apparent ↑

#### Prior Works

- Thread-Level-Speculation (TLS)

- ↓ Apparent

- TLS overhead  $\Rightarrow$  big loops (10× more dependences!)

#### HELIX-RC targets small (hot) loops

- ↑ Code complexity

- Control flow

- Data flow

Prior Works

- Dependences to satisfy  $\uparrow$

- Actual

- Apparent ↑

- Thread-Level-Speculation (TLS)

- ↓ Apparent

- TLS overhead  $\Rightarrow$  big loops (10× more dependences!)

#### HELIX-RC targets small (hot) loops

•  $\Downarrow$  Code complexity

- ↑ Code complexity

- Control flow

- Data flow

Prior Works

- Thread-Level-Speculation (TLS)

- ↓ Apparent

- TLS overhead  $\Rightarrow$  big loops (10× more dependences!)

#### HELIX-RC targets small (hot) loops

- $\Downarrow$  Code complexity

- $\Downarrow$  *Apparent* (only 1.2× more dependences))

Dependences to satisfy  $\uparrow$

Actual

● Apparent ↑

- ↑ Code complexity

- Control flow

- Data flow

Prior Works

- Thread-Level-Speculation (TLS)

- ↓ Apparent

- TLS overhead  $\Rightarrow$  big loops (10× more dependences!)

#### HELIX-RC targets small (hot) loops

- $\Downarrow$  Code complexity

- $\Downarrow$  *Apparent* (only 1.2× more dependences))

- Actual

- Apparent ↑

- ↑ Code complexity

- Control flow

- Data flow

Prior Works

- Thread-Level-Speculation (TLS)

- ↓ Apparent

- TLS overhead  $\Rightarrow$  big loops (10× more dependences!)

#### HELIX-RC targets small (hot) loops

- $\Downarrow$  Code complexity

- $\Downarrow$  *Apparent* (only 1.2× more dependences))

- Enable code transformations to recompute shared values

No TLS

Dependences to satisfy  $\uparrow$

Actual

● Apparent ↑

- ↑ Code complexity

- Control flow

- Data flow

Prior Works

- Thread-Level-Speculation (TLS)

- ↓ Apparent

- TLS overhead  $\Rightarrow$  big loops (10× more dependences!)

#### HELIX-RC targets small (hot) loops

- $\Downarrow$  Code complexity

- $\Downarrow$  *Apparent* (only 1.2× more dependences))

- Enable code transformations to recompute shared values

- ↓ Actual

- Actual

- Apparent ↑

No TLS

## Outline

• Evaluation of HELIX-RC

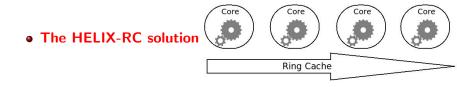

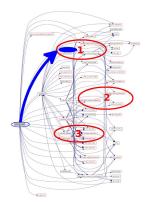

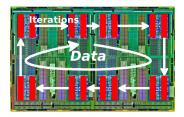

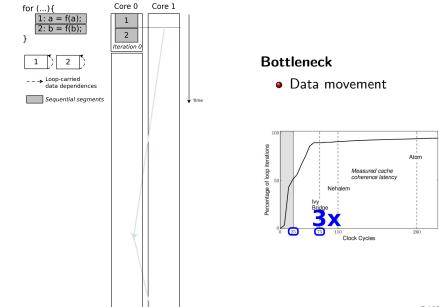

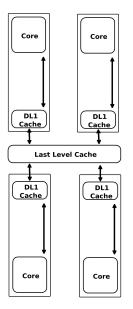

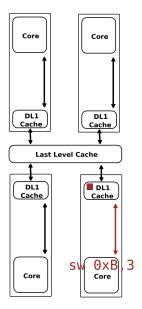

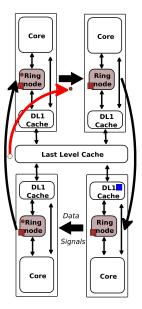

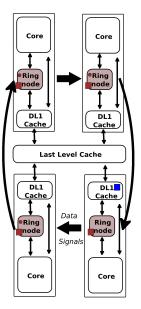

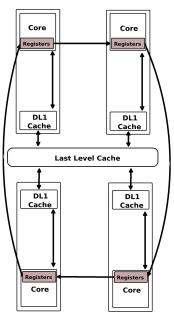

## Split the Work Among Compiler and Architecture

## Split the Work Among Compiler and Architecture

#### Compiler: HCCv3

• Identify code that may generate shared data

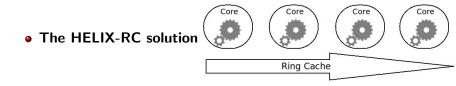

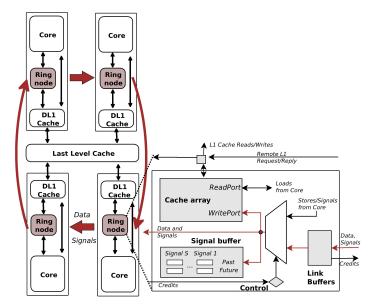

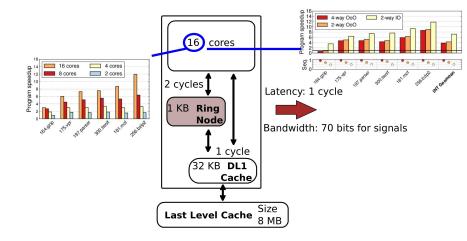

#### Architecture: Ring Cache

#### Compiler: HCCv3

- Identify code that may generate shared data

- Expose information to architecture

#### Architecture: Ring Cache

#### Compiler: HCCv3

- Identify code that may generate shared data

- Expose information to architecture

#### Architecture: Ring Cache

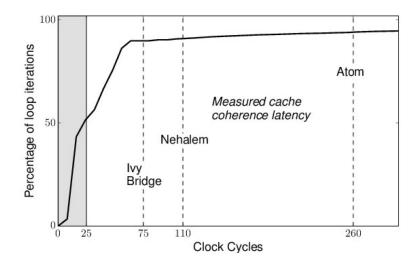

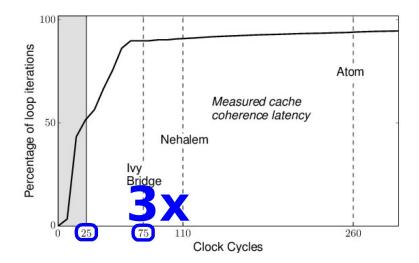

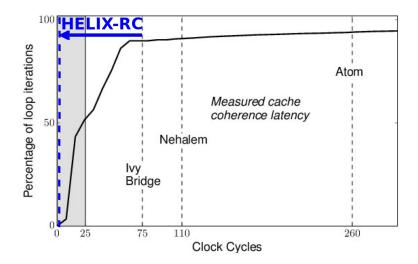

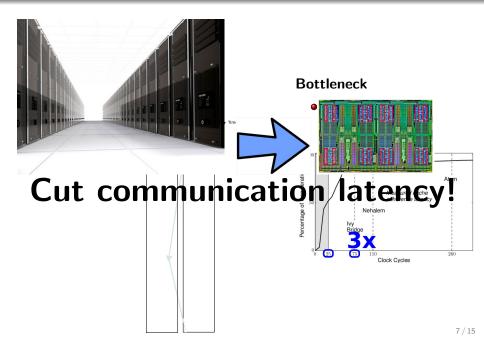

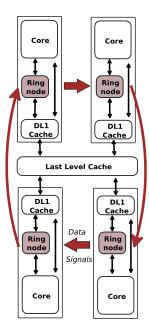

Drastically reduce the communication latency

#### Compiler: HCCv3

- Identify code that may generate shared data

- Expose information to architecture

#### Architecture: Ring Cache

Drastically reduce the communication latency

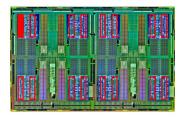

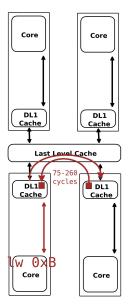

# Traditional coherence protocol

lvy Bridge

#### Compiler: HCCv3

- Identify code that may generate shared data

- Expose information to architecture

#### Architecture: Ring Cache

Drastically reduce the communication latency

• Proactive data distribution

#### Compiler: HCCv3

- Identify code that may generate shared data

- Expose information to architecture

#### Architecture: Ring Cache

Drastically reduce the communication latency

• Proactive data distribution

#### Compiler: HCCv3

- Identify code that may generate shared data

- Expose information to architecture

#### Architecture: Ring Cache

Drastically reduce the communication latency

• Proactive data distribution

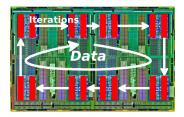

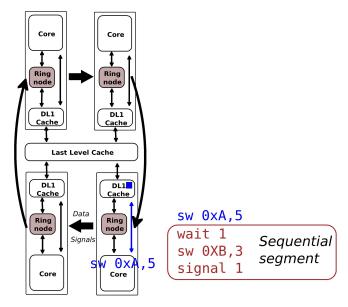

- Identify code that may generate shared loop iteration data

- Keep shared data in memory

- Identify code that may generate shared loop iteration data

- Keep shared data in memory

- Identify code that may generate shared loop iteration data

- Keep shared data in memory

- Identify code that may generate shared loop iteration data

- Keep shared data in memory

- Identify code that may generate shared loop iteration data

- Keep shared data in memory

- Identify code that may generate shared loop iteration data

- Keep shared data in memory

- Identify code that may generate shared loop iteration data

- Keep shared data in memory

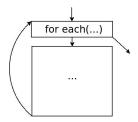

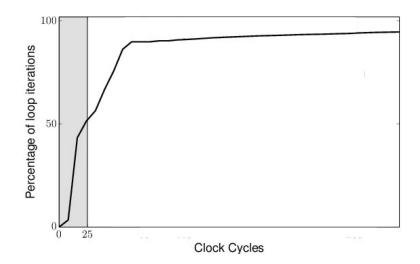

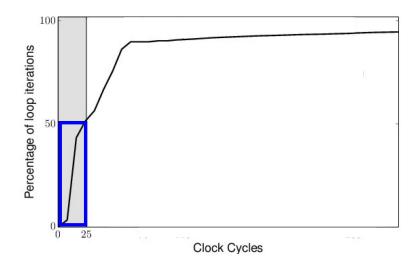

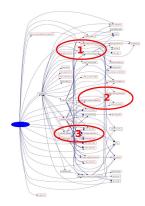

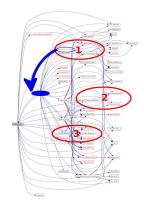

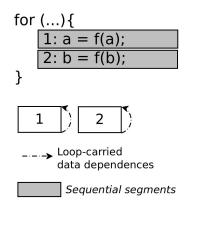

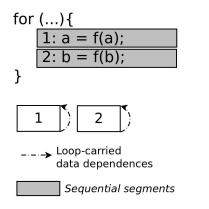

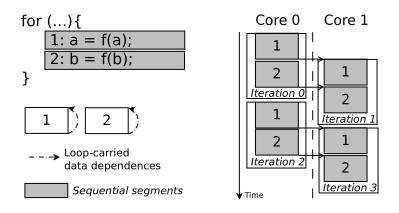

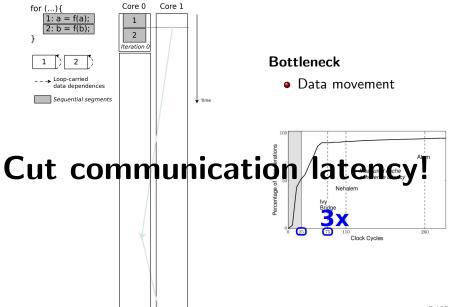

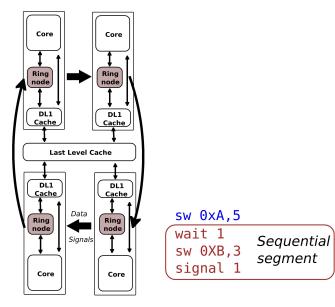

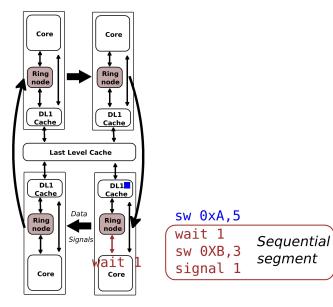

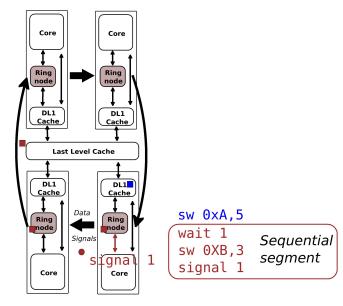

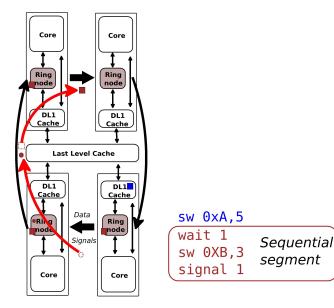

#### • A small loop

• Sequential segments

• Sequential segments *may* generate shared data

- Sequential segments *may* generate shared data

- Each sequential segment executes in loop-iteration order

- Sequential segments may generate shared data

- Each sequential segment executes in loop-iteration order

- Parallelism among sequential segments

#### Bottleneck

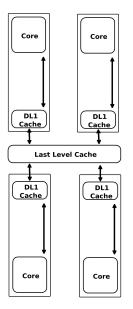

• Data movement

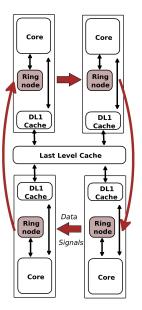

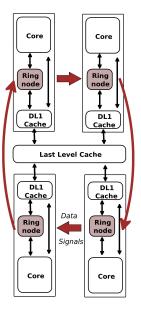

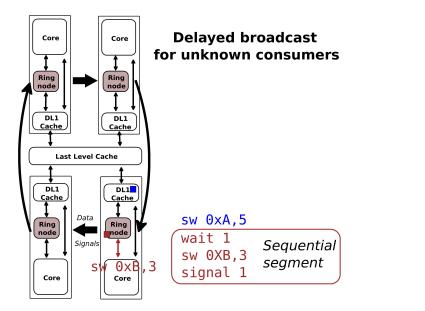

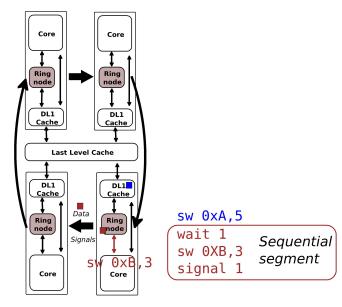

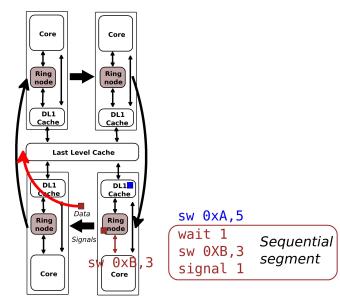

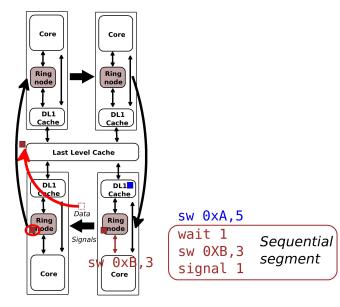

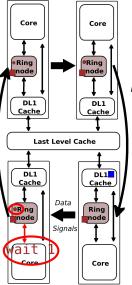

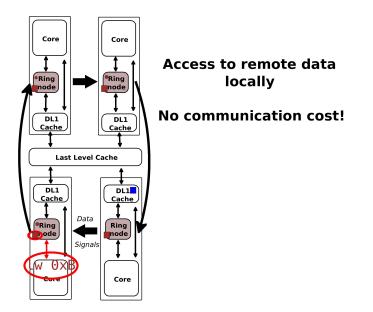

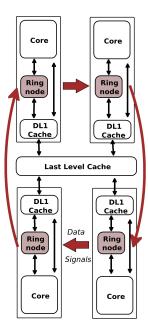

# Ring nodes cache shared data

Accelerate communication shaped by the compiler

#### Core synchronization

#### No communication cost!

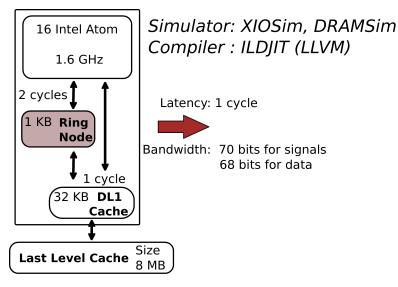

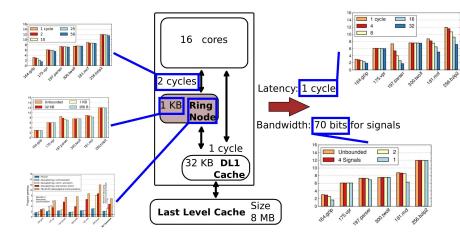

#### Architecture Parameters

"XIOSim:Power-performance Modeling of Mobile x86 Cores" ISLPED 2012, Svilen Kanev et al.]

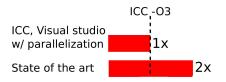

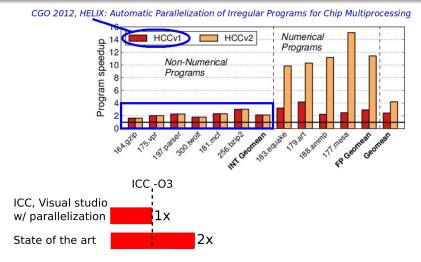

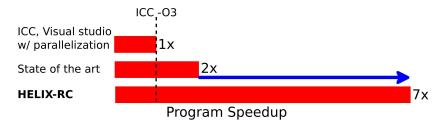

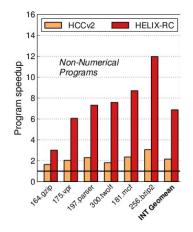

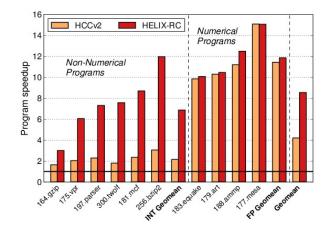

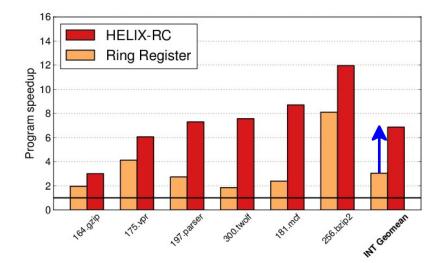

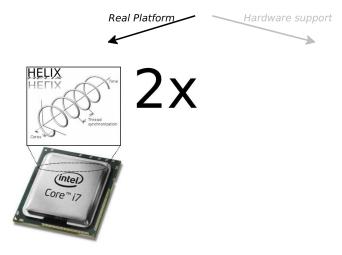

• Compiler-architecture co-design is effective for *non-numerical* workloads

- Compiler-architecture co-design is effective for *non-numerical* workloads

- 3 < speedup < 12

- Compiler-architecture co-design is effective for *non-numerical* workloads

- 3 < speedup < 12

- No slowdown!

- Compiler-architecture co-design is effective for *non-numerical* workloads

- 3 < speedup < 12

- No slowdown!

# Ring Cache vs. Ring Register

# Ring Cache vs. Ring Register

#### Ring Cache vs. Ring Register

#### The Importance of a Cache-Based Scheme

#### **Ring Cache Parameter Analysis**

#### Core Parameters Analysis

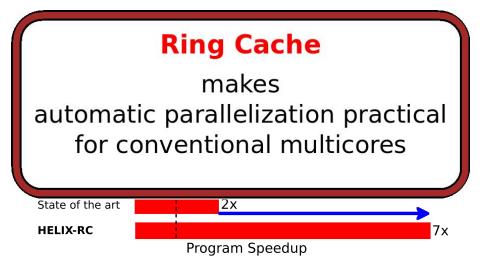

# **Ring Cache**

# makes automatic parallelization practical for conventional multicores

#### HELIX-RC

- $\bullet$  Small loops  $\Rightarrow$  few frequent dependences

- Cut communication latency

- $\bullet\,$  Proactive data forwarding  $\Rightarrow {\sim}0$  communication latency

#### HELIX-RC

- $\bullet$  Small loops  $\Rightarrow$  few frequent dependences

- Cut communication latency

- $\bullet\,$  Proactive data forwarding  $\Rightarrow {\sim}0$  communication latency

# Questions?

http://helix.eecs.harvard.edu

We will release binaries for both

http://helix.eecs.harvard.edu