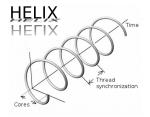

### The HELIX Project: Overview and Directions

Simone Campanoni, Timothy M. Jones, Glenn Holloway Gu-Yeon Wei, David Brooks

Image: Image:

- The HELIX Research Project

- HELIX on commodity processors

- Adaptive HELIX

### Project Goal

Simone Campanoni HELIX 3/23

・ロト ・四ト ・ヨト ・ヨト

æ

A D > A D > A D

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

문 > 문

Simone Campanoni HELIX 3/23

A B >

A

B >

A

A

B >

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

-

< 17 ►

Image: A mathematic state in the state in

Image: A mathematic state in the state in

Simone Campanoni HELIX 3/23

< 17 > 4

Instead of

#### • Software engineer

< 17 > <

- Software engineer

- Compilers

< 17 ►

- Software engineer

- Compilers

- Computer architecture

- Software engineer

- Compilers

- Computer architecture

- VLSI

Instead of

- Software engineer

- Compilers

- Computer architecture

- VLSI

Instead of

- Software engineer

- Compilers

- Computer architecture

- VLSI

A B +

A B +

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

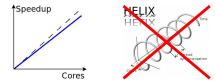

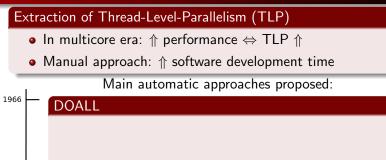

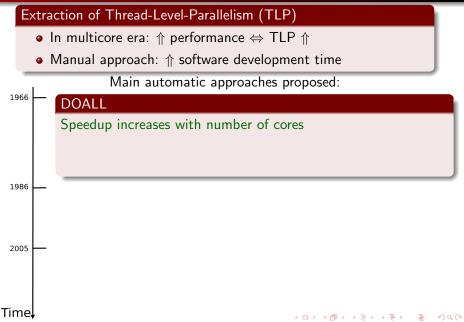

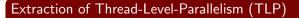

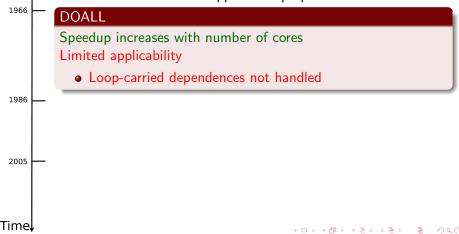

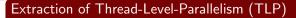

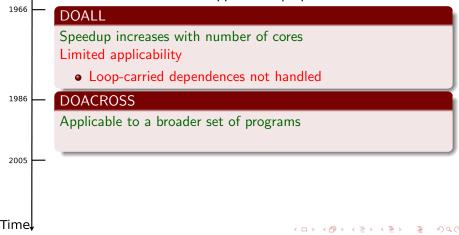

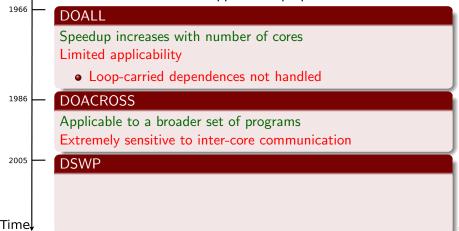

Extraction of Thread-Level-Parallelism (TLP)

イロト イヨト イヨト イヨト

Э

Extraction of Thread-Level-Parallelism (TLP)

• In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

æ

Extraction of Thread-Level-Parallelism (TLP)

• In multicore era:  $\uparrow$  performance  $\Leftrightarrow$  TLP  $\uparrow$

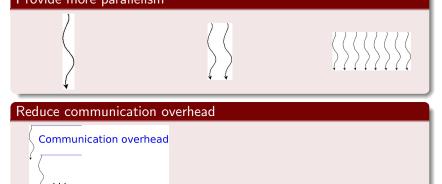

#### Provide more parallelism

< □ > < □ > < □</p>

문 > 문

• In multicore era:  $\uparrow$  performance  $\Leftrightarrow$  TLP  $\uparrow$

#### Provide more parallelism

< □ > < □ > < □</p>

æ

• In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

#### Provide more parallelism

Image: A math a math

# Motivation Extraction of Thread-Level-Parallelism (TLP) ● In multicore era: ↑ performance ⇔ TLP ↑ Provide more parallelism

Simone Campanoni HELIX 4/23

.≞⇒

• In multicore era:  $\uparrow$  performance  $\Leftrightarrow$  TLP  $\uparrow$

#### Provide more parallelism

#### Reduce communication overhead

◆□▶ ◆圖▶ ◆厘▶ ◆厘▶

• In multicore era:  $\uparrow$  performance  $\Leftrightarrow$  TLP  $\uparrow$

#### Provide more parallelism

#### Reduce communication overhead

イロト イヨト イヨト

• In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

#### Provide more parallelism

#### Reduce communication overhead

#### $Parallelism \Leftrightarrow communication$

#### Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\uparrow$  performance  $\Leftrightarrow$  TLP  $\uparrow$

- Manual approach:  $\Uparrow$  software development time

A ₽

#### Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach: ↑ software development time

Automatic approaches target loops

Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach: ↑ software development time

Automatic approaches target loops

• General rule:

90% of the execution is spent in

10% of the code

Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

Automatic approaches target *loops*

• General rule:

more than 90% of the execution is spent in less than 10% of the code

Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\uparrow$  performance  $\Leftrightarrow$  TLP  $\uparrow$

- Manual approach:  $\Uparrow$  software development time

Automatic approaches target loops

• General rule:

more than 90% of the execution is spent in less than 10% of the code

• 10% of the code = hot *loops*

Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\uparrow$  performance  $\Leftrightarrow$  TLP  $\uparrow$

- Manual approach:  $\Uparrow$  software development time

Automatic approaches target loops

• General rule:

more than 90% of the execution is spent in less than 10% of the code

• 10% of the code = hot *loops*

• Our analysis:

Covering  $\geq$  98% of program by selecting loops properly is possible

#### Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach:  $\Uparrow$  software development time

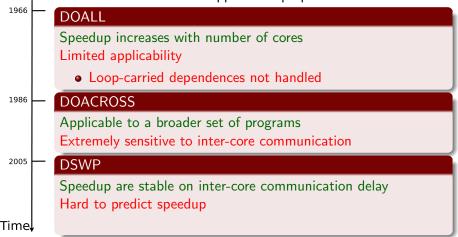

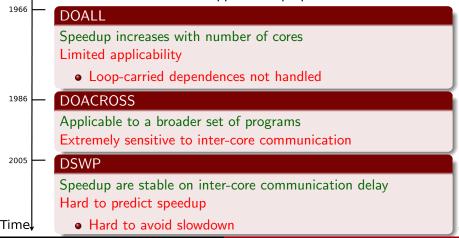

Main automatic approaches proposed:

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

Main automatic approaches proposed:

A ₽

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

Main automatic approaches proposed:

• Manual approach:  $\Uparrow$  software development time

Main automatic approaches proposed:

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

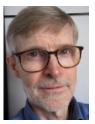

Time

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach: ↑ software development time

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach:  $\Uparrow$  software development time

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach:  $\Uparrow$  software development time

### Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach: ↑ software development time

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

### Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach:  $\Uparrow$  software development time

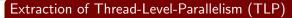

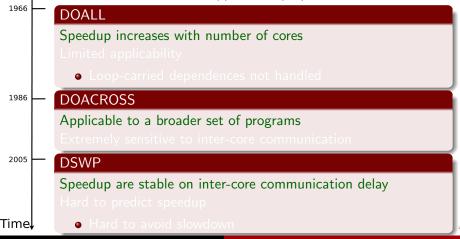

Main automatic approaches proposed:

Is there a way to achieve all of these?

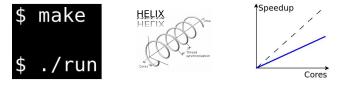

Speedup increases with number of cores

Applicable to a broader set of programs

Speedup are stable on inter-core communication delay

### Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach:  $\Uparrow$  software development time

Main automatic approaches proposed:

Is there a way to achieve all of these?

Speedup increases with number of cores

Applicable to a broader set of programs

Speedup are stable on inter-core communication delay

Produce predictable speedup

### Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach:  $\Uparrow$  software development time

Main automatic approaches proposed:

HELIX

Speedup increases with number of cores

Applicable to a broader set of programs

Speedup are stable on inter-core communication delay

Produce predictable speedup

### Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach:  $\Uparrow$  software development time

Main automatic approaches proposed:

HELIX

Speedup increases with number of cores

General purpose technique

Speedup are stable on inter-core communication delay

Produce predictable speedup

### Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach:  $\Uparrow$  software development time

Main automatic approaches proposed:

HELIX

Speedup increases with number of cores

General purpose technique

Speedup are stable on inter-core communication delay

Produce speedup predictable enough to avoid slowdown

### Extraction of Thread-Level-Parallelism (TLP)

- In multicore era:  $\Uparrow$  performance  $\Leftrightarrow$  TLP  $\Uparrow$

- Manual approach:  $\Uparrow$  software development time

Main automatic approaches proposed:

HELIX

Speedup increases with number of cores

General purpose technique

DOACROSS < Stability of speedup < DSWP

Produce speedup predictable enough to avoid slowdown

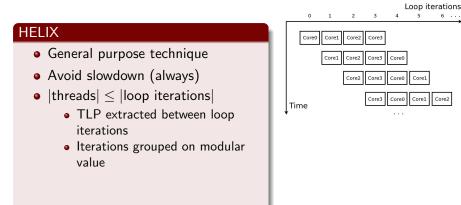

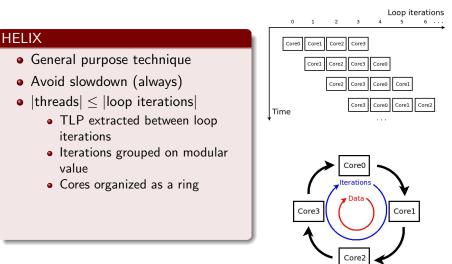

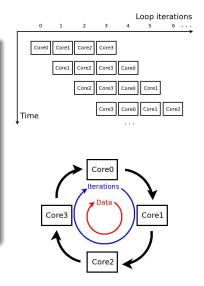

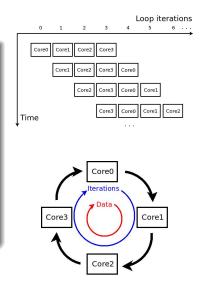

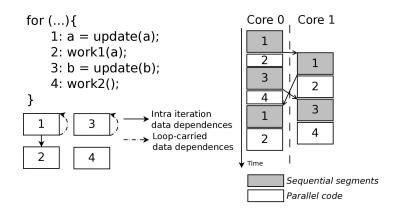

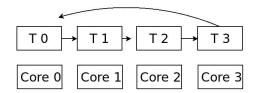

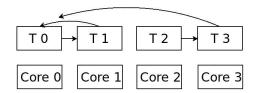

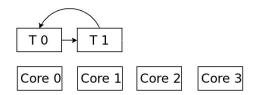

### HELIX

- General purpose technique

- Avoid slowdown (always)

- $|\text{threads}| \le |\text{loop iterations}|$

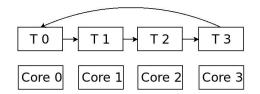

- TLP extracted between loop iterations

Image: A mathematic state in the state in

- General purpose technique

- Avoid slowdown (always)

- $|\text{threads}| \leq |\text{loop iterations}|$

- TLP extracted between loop iterations

- Iterations grouped on modular value

- Cores organized as a ring

- Automatic selection of loops

< 17 >

### HELIX

- General purpose technique

- Avoid slowdown (always)

- $|\text{threads}| \leq |\text{loop iterations}|$

- TLP extracted between loop iterations

- Iterations grouped on modular value

- Cores organized as a ring

- Automatic selection of loops

- Easy to implement

< 17 >

### HELIX

- General purpose technique

- Avoid slowdown (always)

- $|\text{threads}| \le |\text{loop iterations}|$

- TLP extracted between loop iterations

- Iterations grouped on modular value

- Cores organized as a ring

- Automatic selection of loops

- Easy to implement

- Motivation

- The HELIX Research Project

- HELIX on commodity processors

- Adaptive HELIX

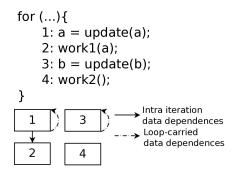

```

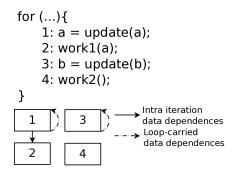

for (...){

1: a = update(a);

2: work1(a);

3: b = update(b);

4: work2();

}

```

```

• A simple program

```

э

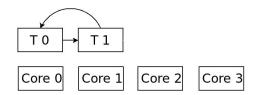

### • Loop-carried data dependences

#### • Idea: exploit independent instructions

< D > < B >

#### • Idea: exploit independent instructions and

< D > < B >

• Idea: exploit independent instructions and

parallelism among sequential segments

• Idea: exploit independent instructions and

parallelism among sequential segments

Problem: amount of synchronization required increases drastically!

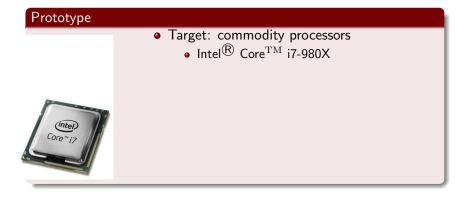

### Prototype

Simone Campanoni HELIX 9/23

æ

・ロト ・回ト ・ヨト

문 🛌 문

### Prototype

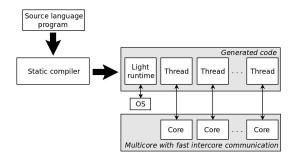

Target: commodity processors

Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

・ロン ・四 と ・ ヨン ・ ヨン

Э

### Prototype

- Target: commodity processors

- Intel $^{\mathbb{R}}$  Core<sup>TM</sup> i7-980X

- Static code generation

・ロト ・回ト ・ヨト

문 > 문

### Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

< D > < B >

### Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

### Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

- Constrain communication overhead

### Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

- Constrain communication overhead

### Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

- Constrain communication overhead

[ CGO 2012, IEEE Micro 2012 ]

### Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

- Constrain communication overhead

[ CGO 2012, IEEE Micro 2012 ]

## Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

- Constrain communication overhead

[ CGO 2012, IEEE Micro 2012 ]

## Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

- Constrain communication overhead

[ CGO 2012, IEEE Micro 2012 ]

Hardware support

9/23

Hardware support

HELIX

Simone Campanoni

## Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

- Constrain communication overhead

[ CGO 2012, IEEE Micro 2012 ]

Hardware support

$$\rightarrow$$

Hardware support

• Push HELIX to the limit

## Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

- Constrain communication overhead

[ CGO 2012, IEEE Micro 2012 ]

## Hardware support

- Push HELIX to the limit

- Minor changes to commodity processors

9/23

## Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

Adaptive HELIX

Simone Campanoni

- Number of cores decided at compile time

- Challenge: achieve speedup

HELIX

• Constrain communication overhead

9/23

・ロト ・回ト ・ヨト

∃ >

Adaptive HELIX

## Prototype

Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

- Constrain communication overhead

## Prototype

- Target: commodity processors

- Intel<sup>®</sup> Core<sup>TM</sup> i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

- Constrain communication overhead

## Prototype

- Target: commodity processors

- Intel  $^{\textcircled{R}}$  Core  $^{TM}$  i7-980X

- Static code generation

- Number of cores decided at compile time

- Challenge: achieve speedup

- Constrain communication overhead

- Motivation

- The HELIX Research Project

- HELIX on commodity processors

- Adaptive HELIX

A B +

A B +

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

A

#### Overhead

#### Optimizations

### Signalling

Notify threads

#### Adopted solutions

Simone Campanoni HELIX 11/23

・ロト ・回ト ・ヨト

< ∃ >

Э

#### Overhead

### Signalling

Notify threads

### Optimizations

#### Adopted solutions

• New code analysis to reduce the number of signals to send

• • • • •

### Overhead

### Signalling

Notify threads

### Optimizations

#### Adopted solutions

- New code analysis to reduce the number of signals to send

- Code scheduling and use of SMT to reduce the delay per signal

### Overhead

### Signalling

Notify threads

## Data forwarding

Forward data between threads

## Optimizations

#### Adopted solutions

- New code analysis to reduce the number of signals to send

- Code scheduling and use of SMT to reduce the delay per signal

### Overhead

### Signalling

Notify threads

## Data forwarding

Forward data between threads

## Optimizations

#### Adopted solutions

- New code analysis to reduce the number of signals to send

- Code scheduling and use of SMT to reduce the delay per signal

- Automatic selection of loops

### Overhead

#### Signalling

Notify threads

## Data forwarding

Forward data between threads

## Optimizations

#### Adopted solutions

- New code analysis to reduce the number of signals to send

- Code scheduling and use of SMT to reduce the delay per signal

- Automatic selection of loops

### Approach

Select loops to parallelize

### Overhead

### Signalling

Notify threads

## Data forwarding

Forward data between threads

## Optimizations

#### Adopted solutions

- New code analysis to reduce the number of signals to send

- Code scheduling and use of SMT to reduce the delay per signal

- Automatic selection of loops

### Approach

- Select loops to parallelize

- $\bullet~\mbox{Each loop} \in \mbox{program}$  is analyzed independently

- These analysis are merged to identify the most profitable loops

- Light off line profile based selection

### Overhead

### Signalling

Notify threads

## Data forwarding

Forward data between threads

## Optimizations

#### Adopted solutions

- New code analysis to reduce the number of signals to send

- Code scheduling and use of SMT to reduce the delay per signal

- Automatic selection of loops

### Approach

- Select loops to parallelize

- $\bullet~\mbox{Each loop} \in \mbox{program}$  is analyzed independently

- These analysis are merged to identify the most profitable loops

- Light off line profile based selection

- Parallelize one loop at a time

## Overhead

### Signalling

Notify threads

## Data forwarding

Forward data between threads

## Optimizations

#### Adopted solutions

- New code analysis to reduce the number of signals to send

- Code scheduling and use of SMT to reduce the delay per signal

- Automatic selection of loops

## Approach

- Select loops to parallelize

- $\bullet~\mbox{Each loop} \in \mbox{program}$  is analyzed independently

- These analysis are merged to identify the most profitable loops

- Light off line profile based selection

- Parallelize one loop at a time

- Each loop uses all cores decided at compile time

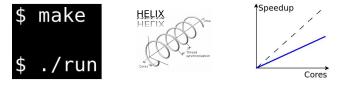

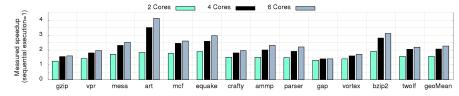

## HELIX on Commodity Processors: Evaluation

#### Platform

- Intel  $^{\ensuremath{\mathbb{R}}}$  Core  $^{\mathrm{TM}}$  i7-980X with six cores

- Each operating at 3.33 GHz, with Turbo Boost disabled

- Three cache levels

- The first two, 32KB and 256KB, are private to each core

- All cores share the last level 12MB cache

#### Platform

- $\bullet~\mbox{Intel}^{\ensuremath{\mathbb{R}}}$  Core  $^{\rm TM}$  i7-980X with six cores

- Each operating at 3.33 GHz, with Turbo Boost disabled

- Three cache levels

- The first two, 32KB and 256KB, are private to each core

- All cores share the last level 12MB cache

#### Benchmarks

C benchmarks from SPEC CPU2000

#### Platform

- $\bullet~{\sf Intel}^{\textcircled{R}}~{\sf Core}^{{\rm TM}}$  i7-980X with six cores

- Each operating at 3.33 GHz, with Turbo Boost disabled

- Three cache levels

- The first two, 32KB and 256KB, are private to each core

- All cores share the last level 12MB cache

#### Benchmarks

C benchmarks from SPEC CPU2000

#### Compiler

● HELIX has been implemented ∈ static compiler ILDJIT

Overall program speedup

- 4 🗇 🕨 - 4 🖹

## Speedup Obtained on a Real System

#### Overall program speedup

Notice: no slowdown

æ

- Motivation

- The HELIX Research Project

- HELIX on commodity processors

- Adaptive HELIX

• Code produced for N cores

・ロト ・回ト ・目と

문 > 문

# Adaptive HELIX

- Code produced for N cores

- The number of cores changes to M at run time

- Performance

- Multi-programs scenario

# Adaptive HELIX

- Code produced for N cores

- The number of cores changes to M at run time

- Performance

- Multi-programs scenario

<ロ> (日) (日) (日) (日) (日)

æ

・ロト ・回ト ・ヨト

≣ >

A (10) < A (10)</p>

<- ↓ ↓ < ≥ >

문 > 문

A (10) < A (10)</p>

A (10) > (10)

A (10) > (10)

<- ↓ ↓ < ≥ >

문 > 문

• Few store instructions

A (10) > (10)

- Few store instructions

- Thread management

< 177 ▶

What is the cost of adapting the produced binary?

- Few store instructions

- Thread management

- Thread pool

< 177 ▶

Simone Campanoni HELIX 17/23

æ

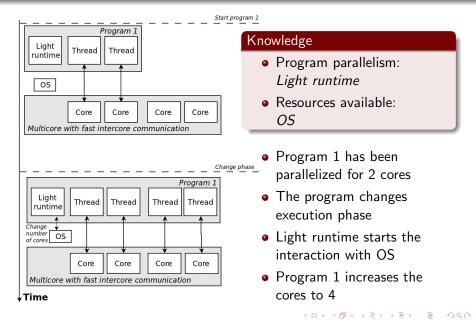

• Programs have execution phases

< □ > < @ > < 注

- Programs have execution phases

- Different executed paths

< 17 >

- Programs have execution phases

- Different executed paths

- The amount of parallelism of a loop changes over time

- Programs have execution phases

- Different executed paths

- The amount of parallelism of a loop changes over time

- Number of cores to target are adapted at run time

- Programs have execution phases

- Different executed paths

- The amount of parallelism of a loop changes over time

- Number of cores to target are adapted at run time

<ロ> (日) (日) (日) (日) (日)

э

Simone Campanoni HELIX 18/23

Э

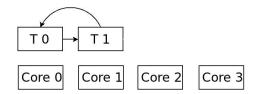

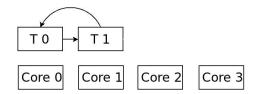

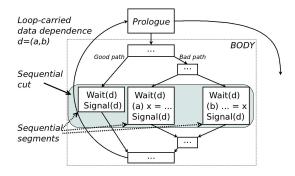

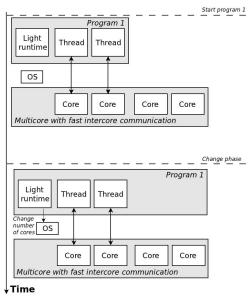

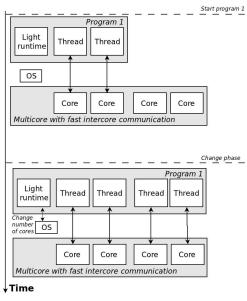

- Program 1 has been parallelized for 2 cores

- The program changes execution phase

Image: A match a ma

문 > 문

#### Time

- Program 1 has been parallelized for 2 cores

- The program changes execution phase

- Light runtime starts the interaction with OS

Image: A match a ma

• E •

æ

- Program 1 has been parallelized for 2 cores

- The program changes execution phase

- Light runtime starts the interaction with OS

- Program 1 increases the cores to 4

イロト イポト イヨト イヨト

æ

Time

Simone Campanoni HELIX 19/23

<ロ> (日) (日) (日) (日) (日)

Э

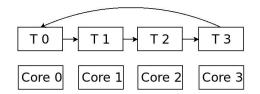

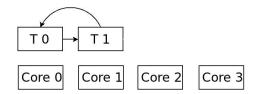

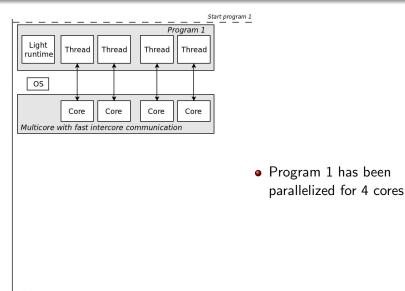

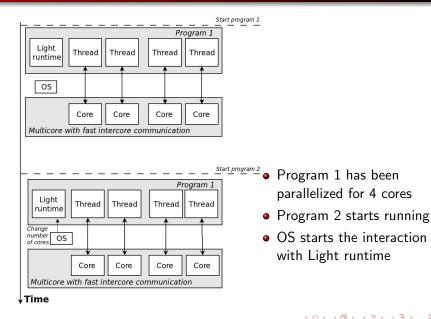

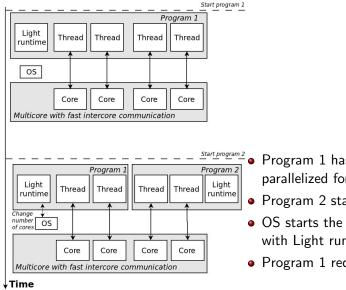

- Program 1 has been parallelized for 4 cores

- Program 2 starts running

・ロト ・回ト ・ヨト

• E •

æ

#### Time

æ

- Program 1 has been parallelized for 4 cores

- Program 2 starts running

- OS starts the interaction with Light runtime

- Program 1 reduces the cores

▲ □ ► ▲ □ ►

3 D

Program 1 has been parallelized for 4 cores

- Program 2 starts running

- OS starts the interaction with Light runtime

- Program 1 reduces the cores

▲ □ ► ▲ □ ►

æ

- 4 ⊒ >

Image: A math the second se

• Significant speedups can be achieved on current hardware

- Significant speedups can be achieved on current hardware

- Hardware not designed for this type of execution

- Slowdowns are always avoided

- Significant speedups can be achieved on current hardware

- Hardware not designed for this type of execution

- Slowdowns are always avoided

- HELIX is able to run both independent and most of dependent code in parallel

- Significant speedups can be achieved on current hardware

- Hardware not designed for this type of execution

- Slowdowns are always avoided

- HELIX is able to run both independent and most of dependent code in parallel

- The HELIX code is adapted at run time

- for performance

- to handle multiple programs

#### Light runtime and OS extension is required

æ

・ロン ・回 と ・ ヨン ・ ヨン

#### Websites

- HELIX

- http://helix.eecs.harvard.edu

- http://twitter.com/#!/Helix\_project

<ロ> (日) (日) (日) (日) (日)

æ

#### ILDJIT

http://ildjit.sourceforge.net

#### Email

xan@eecs.harvard.edu

# Thanks for your attention!

Image: A math the second se